Skip to the content

Recent

Work:

- Working on 25G Ethernet channel design

- 10G Ethernet board, <1E-15 BER

- 32 lane PCIe Gen 3 VPX channel design, <1E-12 BER

- DDR3L dual rank 1866 custom design on 28 layer board

- Xilinx PCIe Gen 3, 10G Serdes development

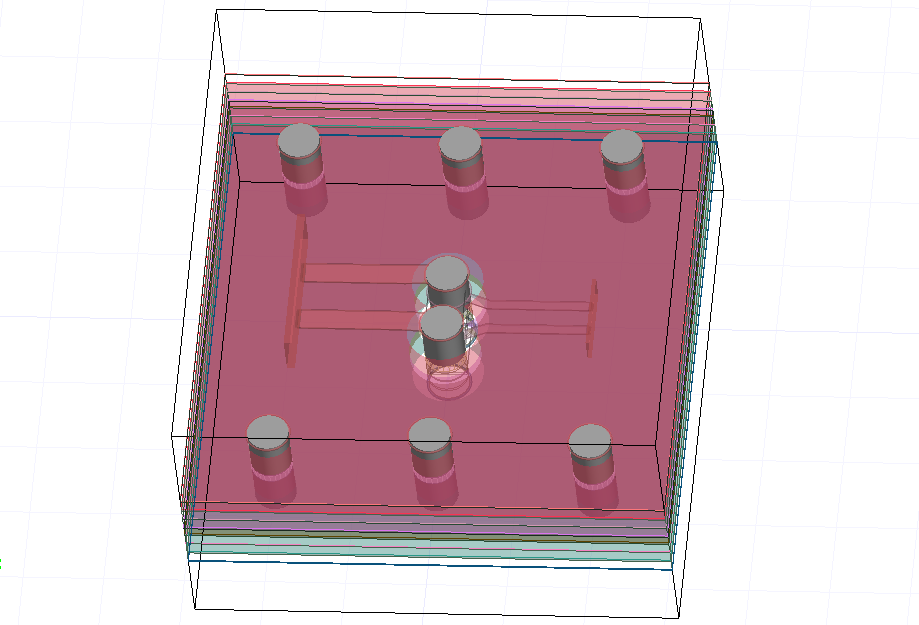

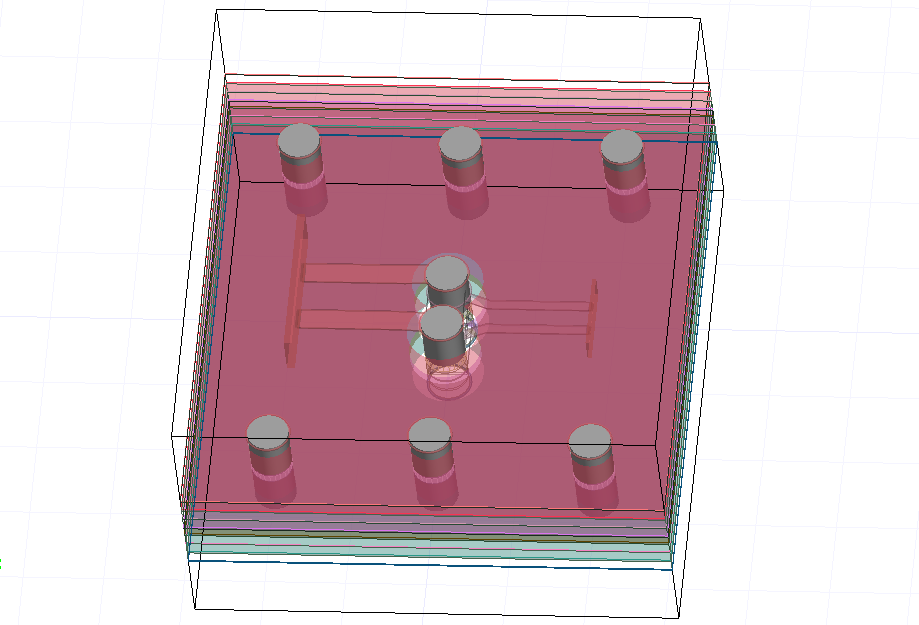

- Power Integrity analysis using Ansys SiWave and HSFS

- EMI/Resonance minimizations using Ansys SiWave

- FPGA/CPU single board computer boards

- VHDL, Xilinx iBert channel BER determinations

Past

Work:

-

SATA Gen 3 VPX storage modules

-

PCIe Gen 2 VPX switch boards

-

VNA/RTO board and channel comparisons to HFSS simulations

-

Xilinx VHDL development for aircraft control systems

-

VPX Freescale/Xilinx single board computers

-

DDR2 custom design on 24 layer board

Other Info:

- Xilinx high speed constraint class

- Ansys SiWave and HFSS classes

- Syracuse University, MSEE

- PE, Pennsylvania